|

如果同学们的问题我们帖子里面没有的请第一时间联系我微信同步:易老师13112063618(微信同号) |

明德扬最近做了抖音系列短视频,感兴趣可以关注明德扬抖音号:FPGA技巧分享(87481069842)至简书籍短视频(74803215644)

内容不断更新!点赞+关注,学习不迷路!

一、SDRAM和DDR专题课

【问题1.1】DDR3那个课程,一般线速率能跑到多少?答:本课程的DDR3内容,是基于XILINX K7芯片,使用的是VIVADO平台。DDR3的时钟频率是800M。用户侧时钟是200M。

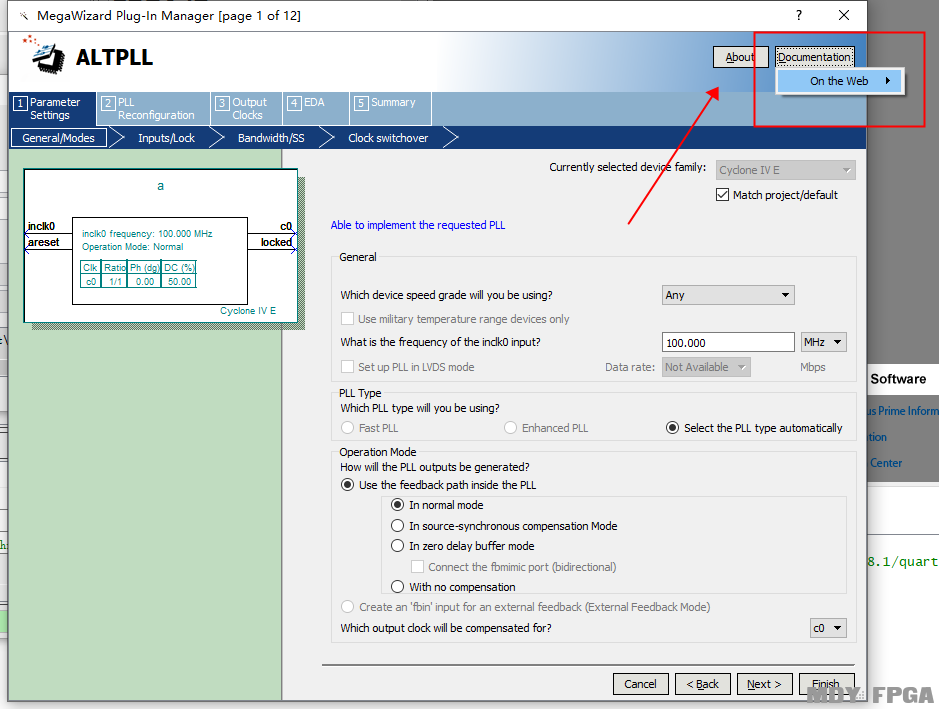

【问题1.2】SDRAM和DDR3课程,使用是什么平台?

答:SDRAM部分使用的是QUARTUS平台,着重于讲解SDRAM时序和SDRAM的接口设计。DDR3部分,使用的是VIVADO平台,着重于DDR3 IP的生成和上板验证流程。

DDR3的理论部分,基本上不涉及,建议可以参考SDRAM的理论部分。

【问题1.3】 使用DDR3 IP一定需要读地址FIFO,读数据FIFO,写地址FIFO,写数据FIFO来先进行数据缓存吗?

答:这个理解是不对的。这里没有跨时间域的信号传输的。因为IP核会产生一个本地时钟,这个本地时钟是可以直接采集数据的,假设为clk_ddr_local。

用户可以直接使用clk_ddr_local来往IP核传输数据。

好了,接下来再考虑一个场景:我有一组数据A,产生于时钟域clk;A要写到DDR,DDR的时钟域是clk_ddr_local。

自然地,A要跟时钟域到clk_ddr_local,然后才能写到DDR中,这就需要用到FIFO。

接下来考虑另一个场景:我有一组数据B,产生于时钟域clk_ddr_local;B要写到DDR,DDR的时钟是clk_ddr_local。

由于两个时钟域相同,直接写就好了。(通常来说,这已经不属于DDR的知识了,而是属于跨时钟域处理的知识,是FPGA工程师都应该知道的概念)。

【问题1.4】用户逻辑控制DDR3读写的程序不是需要自己写吗?答:官方一般提供了DDR3的IP核。

答:用户可以通过DDR3 IP核来进行DDR3芯片的读写。但是用户需要写逻辑来控制DDR3 IP核。

【问题1.5】课程里会讲如何通过DDR3 IP像写入图像吗?

答:课程中的SDRAM部分,会有例子讲如何写入图像到SDRAM中,DDR3/4也是类似的。但由于每人的项目不同,所以需要学员根据自己情况来移植。

【问题1.6】如何知道ddr3里不空,可以读取了?

答:DDR3和RAM一样,是一个存储器件,它的每个内部单元都存储了当前的数据状态值。

但DDR3和RAM本身,是没有“空”、“存有数据”,“数据满”等概念的。只要给地址,它就会把当前地址的数据给到总线上,

而且这个地址可以读很多次。在设计的时候,是由设计师用自己写逻辑来判断DDR3是否为空。

【问题1.7】请问这个sdram的自动刷新命令发送后,是不是刷新的是所有bank的同一行都在执行刷新呀?也就是说刷新的是不同bank的同一行,是不是这样理解

答:是的。发送一个自动刷新命令,所有BANK同一行都会刷新。

【问题1.8】请问有ddr3的IP核手册吗?(altera的)

答:IP核不同,界面会所不同,但一般都会提供下载链接的。VIVADO、ISE等,也是同样的情况

【问题1.9】做一个用到ddr4的项目,有一个ddr3的例程,不知道怎么改成ddr4?

答:百度搜索找资料,按流程配置就好,这个我们没有教程,只能看数据手册

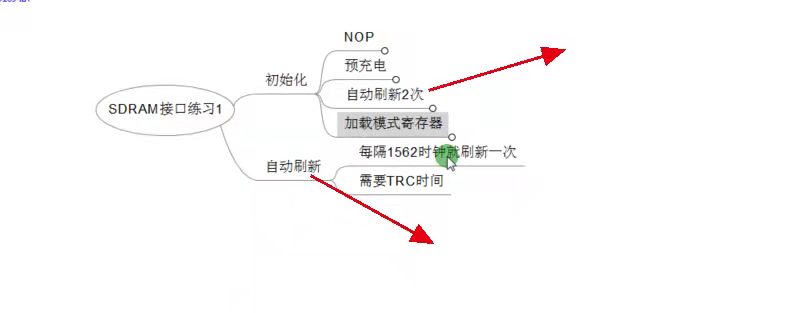

【问题1.10】下图中的自刷新有啥区别?

答:上电后,要经过初始化,初始化中要有两次刷新动作;当初始化完成后,才是每隔一段时间,要自刷新一次

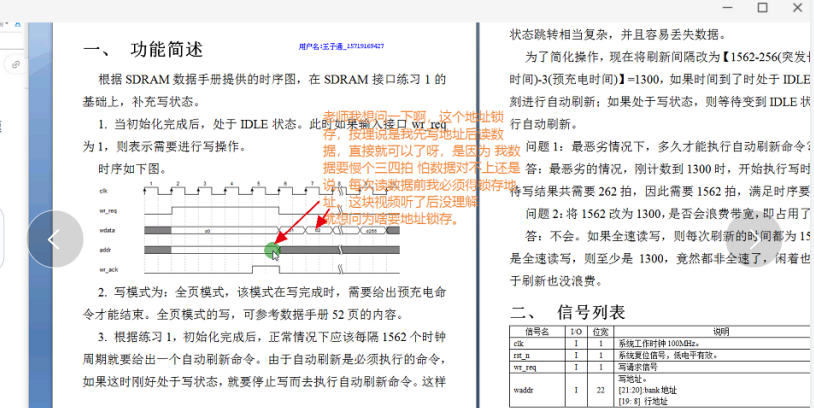

【问题1.11】如下图所示,为什么在接口中,一般要锁存住地址addr、写数据wdata等?不锁存不行吗?

但注意,在第7~10,addr的值还是不是2呢?可能不是了。

【问题1.12】请问连接ddr3 ip核与mem_burst时,有些端口未定义。内些未定义的端口怎么办?

答:

1. 本课程提示的案例,经过上板验证是可以的,如果不可以,请及时向老师反映。

2. 本例程验证过是可以的,因此例化时未连接的信号,就说明对本例程来说不用关心,不用使用。

3. 如果您要想关心这些信号,可以阅读数据手册,了解该信号含义。

【问题1.13】问题:请问老师xilinx FPGA的HR bank的 lvds接口可以驱动250Mhz DDR adc 吗?我一直只能跑到100Mhz ,不知道是不是我的时序有问题?

答:

1、首先请确认使用的芯片是否支持该DDR的速率;

2、如果支持的话,请严格按照设计规范进行设计;

3、同时请检查该开发板的pcb原理图的设计是否合适,例如pcb的走线是否等长,或者pcb的板材是否合适、阻抗是否匹配......

这些都会影响DDR的速率。

【问题1.14】问题: 有 vivado 下 DDR模型和参数不?用于仿真?

解答:解答:vivado DDR可以生成对应的例程,可以用于仿真。具体操作步骤可以百度搜索一下,例如:Xilinx VIVADO中DDR3 IP核的使用(1)_朽月的博客-CSDN博客_xilinx ddr 自动刷新

【问题1.15】问:SDRAM中将刷新时间改为1300的意义何在?

答:如果以1562个为周期,当时间到了之后,如果此时处于写或读操作状态,就要等一段时间再进行刷新操作,这样刷新间隔就会大于1562,不满足要求。

【问题1.16】问:请问在边缘检测的项目中,输入输出数据是25M,SDRAM的工作时钟是100M,这种情况下读写效能是多少呀?

答:SDRAM读写总线效能一般计算:SDRAM的工作时钟 * 数据位宽 *70% 。(注意:其中70%是指减去sdram的一些操作占用后的效能,70%的数值是经验之谈,请根据实际情况变更数值)

【问题1.17】问:SDRAM工程中,读写请求是一个脉冲,还是连续的电平?

答:在MDY自定义的接口中,读写请求是一个持续为高的电平信号,一直拉高直到模块响应为止。拉高一个电平为表示读写一次。

二、高手修炼专题课

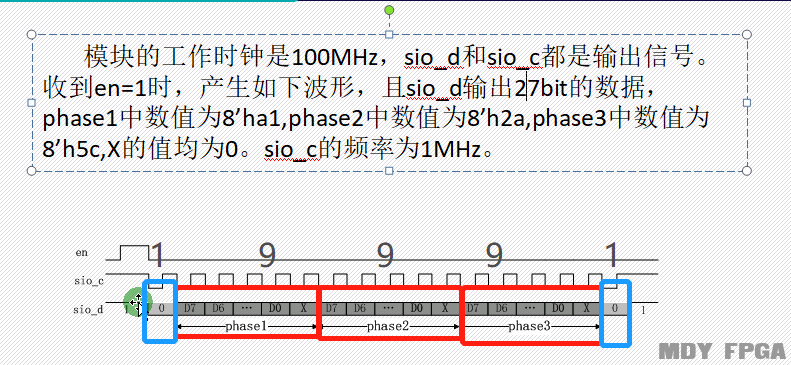

答:数据位一共是27位,开始位1位,结束位1位,还要注意看上图中,第三字节x后还有1位的0,之后才是结束位,所以一共是30位。

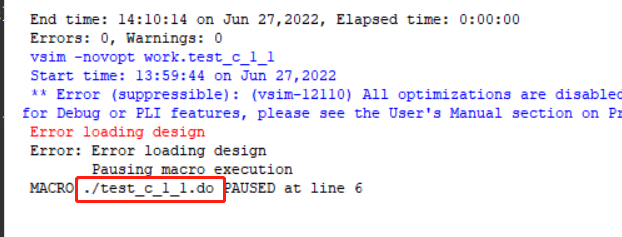

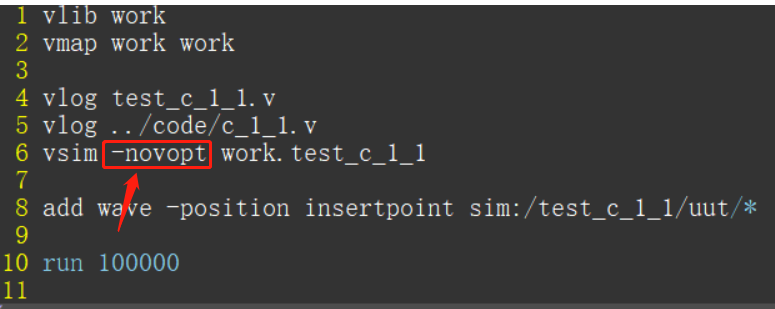

【问题2.2】在高手修炼课中,使用MDY提供的DO文件跑仿真,提示如下错误:

答:这是由于MODELSIM版本不一致导致的。请打开DO文件,去掉下面的-novopt语句。

三、实用调试技巧专题课

问题【3.1】调试技巧训练,signaltap练习1里,我找到了报错的位置,但是我很好奇为什么会出现这个错误:dout没有输出123,连续输出了两个124。

答:这是signalTap工具使用的训练习题,只需要找到错误即可,不用修正错误。并且该练习的设计文件已经封装成IP核了,无法看到内部设计文件,所以不需要纠结练习问题的生成原因。

问题【3.2】调试技巧课程 - 测试文件编写练习3-练习要求中的”报文之间的间隔位3字节“ 是指3个时钟周期?

解答:需要根据报文数据的位宽来确定的。例如,报文数据data位宽为8bits,那么间隔3字节就需要3个时钟周期;假如data是其他位宽,以此类推。

四、FIFO架构设计专题课

【问题4.1】关于FIFO的深度计算问题?

答:可以看此贴:http://old.mdy-edu.com/jishuwenz/2020/0219/914.html

【问题4.2】图中X代表什么意思

这个有效多少是取决于mdy的值(经过FIFO后,即是Q的33和32位)。可以代入数据可以看到x的值。例如:当q[33:32]=1时,表示有1字节无效,即3个字节有效,所以此时x等于3。

【问题4.3】问:FIFO仿真时,与预想的不一样,有时候会出读出的不对?

答:在做FIFO仿真的时候,如果出现仿真出错的情况,建议按如下方式定位。

1. 一定要抓取FIFO的内部信号来观察。注意,一定是内部信号,例如FIFO这个模块的q、rdreq等。

2. 要先确认FIFO的输入端,即wrreq信号和写数据,一个时钟(写时钟)一个时钟去对,最好记录一下这个数据。

3. 其次,确认FIFO的输出端,即读时钟、rdreq和q这三个信号,一个时钟一个时钟去对,把数据记录下来。

4. 最后,再用写数据和读数据进行对比。

另外,一般是不会有问题的,请认真核对。

请注意,有部分同学反馈还是出错,我们技术经过远程定位后,发现同学在确认数据时,没有按时钟一个一个来数,导致了疏忽和遗漏,请确保一定要仔细核对。

【问题4.4】wrusedw是写侧保持数据个数, rdusedw是指读出读出了多个数据个数?

答:无论wrusedw还是rdusedw,均表示FIFO内保存有多少个数据。它们之间的区别仅仅是时钟域不同,wrusedw对应的写时钟域,即与写时钟对齐的信号;

rdusedw对应的是读时钟域,即与读时钟对应的信号。由于写时钟和读时钟频率、相位等不同,所以wrusedw和rdusedw是无法完成一致的,使用时要注意。

五、综合项目实践课——温度检测工程

【问题5.1】温度控制系统:

1.串口进去之后,你有一个ASCII 转Hex的一个模块 ,然后进去之后有将包头解析 里面进入控制模块 可以直接发送hex数据 进入 然后加CRC检验2.原本出来的数据是hex数据也就是说数据出来之后,在上位机去计算一下就好了,反而简单,在这里你又将HEX转换为ASCII 也就是说 你上去之后又很麻烦,而且下面处理也变麻烦了 。直接发送hex去上位机解析就好了 。原本一个简单的小dome最后反而变复杂了。

3.就是原本温度的数据在采集的过程中 可能会有不稳定的情况,你比如在采集的很长的数据中,有突变的,但其实,那个是不稳定的数据。加一个滤波算法进去。这样数据就会很稳定。也让这个小dome变的有意义,因为FPGA主要的就是去做算发 让他发挥他本有的长处,才是最好的做法。

①项目的功能需求各种各样,当然去掉ASCII转换模块更简单,但是有的项目它的需求就是ASCII码操作,所以项目功能的架构最终都要根据需求进行设计。

②然后,我们这个温度检测工程是一个培训项目,所以关于ASCII功能也会加入到项目中用于训练。

③同时,温度检测只是该工程里核心的功能,其他功能的设计同学们也可以根据自己的脑洞想法、自己的需求进行设计体会,我们非常欢迎同学们在群提出和分享自己的思路想法,互相讨论,共同进步。

④当然同学们也可以蹲一下我们不定期开播的潘老师直播间,把自己项目功能设计、架构设计等等的疑问和需求提出来,跟潘老师进行讨论,解决你的问题。

【问题5.2】问:在下面的DS18B20的读时序中,中间部分(即红色框部分),是否指FPGA要输出高电平 ?

答:不正确。该时序前面一段是FPGA输出低电平(dq_out为0,dout_out_en为1)。然后是FPGA释放总线(dq_out_en为0,dq_out不关心)。

在后一段,是DS18B20输出值,FPGA读出值(dq_out_en为0,dq_out不关心。取dq_in的值)。

六、综合项目实践课——边缘检测工程

【问题6.1】点拨开发板,下载工程检测工程后,没有反应。

答:注意:下载后,需要按下矩阵键盘的按键0(即左上角第一个按键),才能显示!!!

【问题6.2】点拨开发板可以显示摄像头拍摄过来的图片吗?

【问题6.3】PCLK的时钟频率问题

也就是说PCLK和XCLK频率大小一样,只是说可能不同相

【问题6.4】是否不使用PLL,而是用PCLK来作为采集模块的时钟?

答:PCLK经过插件连到FPGA,这其中可能会不稳定。为解决此问题,将PCLK连到PLL,产生一个同频同相的时钟,

使用这个时钟作为采集模块的工作时钟。这样,即使PCLK缺少或者不稳定,但产生的时钟也会保持稳定。

【问题6.5】摄像头寄存器配置模块中,配置的是04对应RGB,但是数据手册中RGB应该是01,这是为什么?

RAW RGB:在摄像头里没有经过任何处理的数据。

RGB:在摄像头里经过了ISP等算法处理的数据。

如果想要最原始的数据,就使用RAW格式;如果要摄像头先美化一下,就使用RGB格式。想要哪种格式,取决于您的需求。

【问题6.6】边缘检测寄存器是怎么样配置的呢?

答:边缘检测中,ov7670_cfg模块和sccb模块,就是用来配置的,可以参考

【问题6.7】边缘检查课程案例OV接口是用MIMP还是DVP的?

答:OV7670是标准的SCCB接口,兼容IIC接口

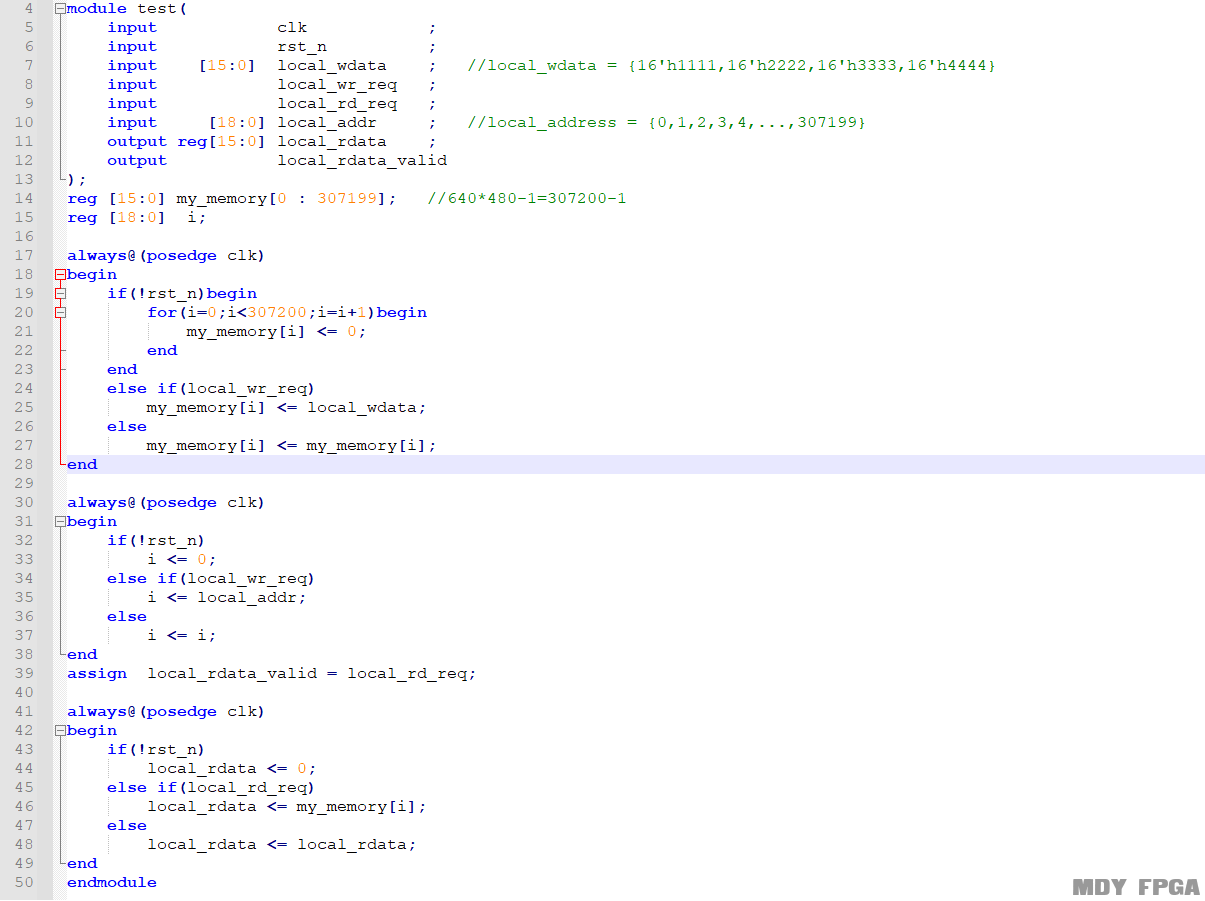

【问题6.8】请问在边缘检测模块中的vga_config模块,如果想显示完整的一帧图像(假设为彩条显示)而ram资源不够,我用的多维数组来做存储器存储16bit 640*480个像素点,

(目的:在local_wr_req时将写数据按地址存进去,在local_rd_req时将数据按地址读出来),请问以下代码方案是否可行,若不行,请问该如何实现此目的?(代码如下图示)

答:

1. 使用二维数组代替RAM方法:二维数据使用的是寄存器资料,通常RAM资源是远远大于寄存器资源的,所以RAM不足时,寄存器一般也不足。

2. 如果只是仿真用途,这个是可以的,可以不考虑资源。既然是仿真,那自然也可以增大RAM了。

3. 注意上面代码中有错误,读写地址是独立,不是共同一个的。读哪些地址数据,无关写地址。上面代码中不正确,具体请仿真。

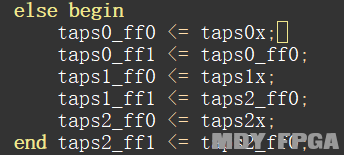

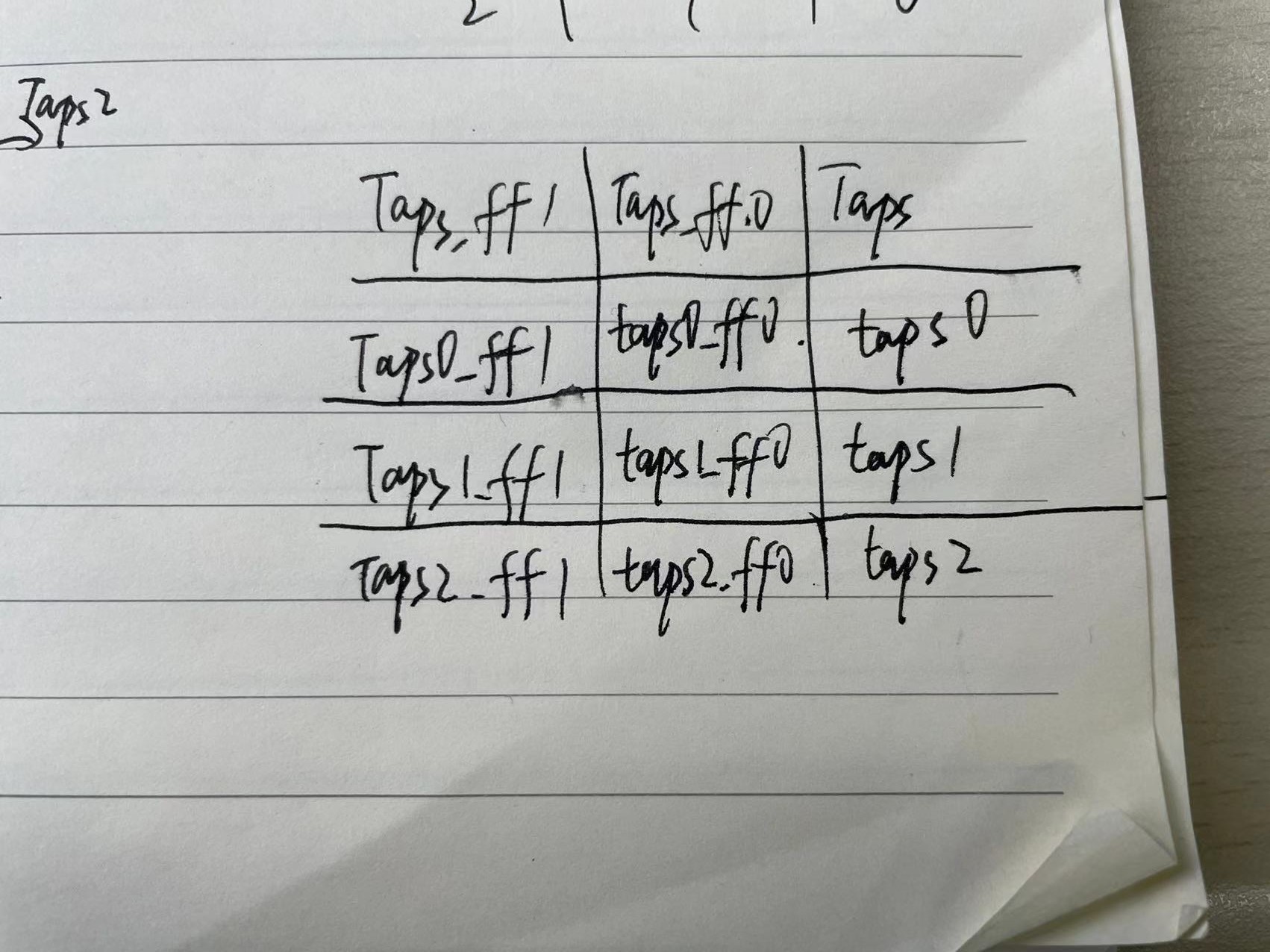

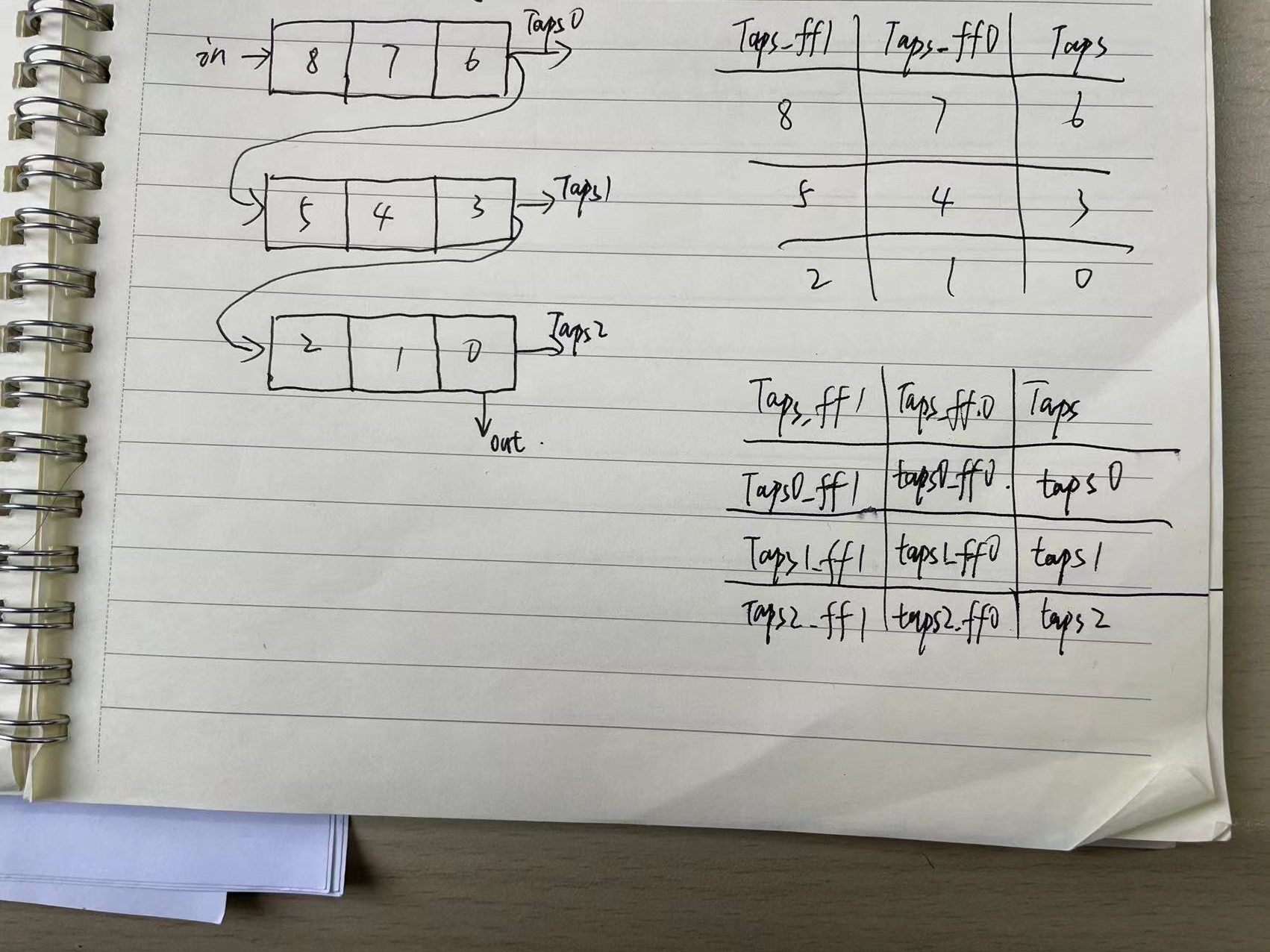

【问题6.9】这个关系怎么得到的呢?根据这个图的话 上面的关系不应该反过来吗?在下一拍的时候应该吧taps0_ff0赋值给taps0x呀?

答:没有 ff0就是表示 延时一拍的意思,taps0_ff是taps0前一时刻的值,需要得到这种结果,就是通过时序逻辑打一拍,资料提供的有直播课讲解,建议结合仿真波形去看,测试文件有提供

【问题6.10】请问这一段写在代码的哪里?我找不到,看不出

答:在SCCB代码里

【问题6.11】 边缘检测课程这个判断读或写使能的计数器的rw_cnt为什么刚好对应add_wdata[16]和add_wdata[17]?

解答:在工作状态(flag==1)时,此时对ov7670的指令进行读写,那到底是对指令进行读还是写,使用读写操作计数器rw_cnt进行计数,按顺序的进行判断。根据模块ov7670_para.v 里指令的格式:{读操作(1bit),写操作(1bit),操作指令(16bits)}。当rw_cnt=0时,设计上此时先判断指令写操作是否有效,因此对应判断ov7670_para.v 里指令的add_wdata[16],确认对应比特位的写操作是否为高电平,如果是,那么需要对该指令进行写操作,产生一个写使能有效信号(wr_en==1)。其他以此类推。

【问题6.12】边缘检测里面的sccb模块中,根据sccb手册要求,读时序的传输周期要写成两段写,为什么代码里面省了第二段(设备地址+读数据)?

这上面读时序传输周期只写了一段。

解答:理解有误,代码里sccb的读操作是有两段时序的。请联系信号 rd_com、count_duan、out_data、flag_sel,直接仿真查看波形一起理解,这样会更直观。

【问题6.13】问:边缘检测工程中,配置ov7670的寄存器顺序是固定,修改顺序要重新修改代码后上电,有没有办法可以不上电直接修改?

答:目前代码就需要重新上电。 不重新上电的方式,就参考温度检测工程,需要上位机配合

【问题6.14】问:边沿检测课程里,VGA_driver里面的行同步场同步信号为什么需要打拍延时产生?

答:在本模块中,使用了行计数器和场计数器来产生了读地址rd_addr。

1. 该地址送给上游模块vga_config,然后将数据返回给本模块会有几个时钟的延时。

2. 为了让返回的数据,与最终的信号vga_vys和vga_hys对齐,所以要延时一下,打了两拍再产生行场同步信号。

3. 具体可以通过整体工程仿真来检查确认。检查返回的第一个数据是否有延时;第一个数据与行场同步信号是否有就是对 。

【问题6.15】边IP核配置代码中,下面部分的 3'b110,8'h02,32'h00800020 110,02分别属于什么功能呢

答:

1. 前面3比特的3'b110用于定义读写属性:分别是表示读、写和等待位。当对应位为1,表示使能。

a. 例如,3'b110,表示读使能、写使能、等待不使能。那么在代码中,将会对寄存器先执行写操作,然后再执行读操作。读操作的目的,是为了检查写的对不对。

b.例如,3'b001,表示读不使能,写不使能,等级使能。在代码中,不对寄存器操作,只用于延时。

2. 中间的8位是读写地址。即寄存器的地址,对应着IP核数据手册中的寄存器地址。

3. 后面的32位是写数据或者延时值。当写寄存器时,是写到寄存器的数据。当读寄存器,不关心,可填充为0。当是延时操作时,表示要延时的值,单位为时钟周期。

【问题6.16】问:请问边缘检测中,对于SDRAM模块的读写,涉及到仲裁内容吗?(边缘检测)

答:涉及到,就是读写怎么判断的问题